ATR statistics: TA3 - Specific to T after T from 0 to 14 in TDi–1

Article from the series "ATR statistics".

TA3 - Specific to T after T from 0 to 14 in TDi–1

The ISO 7816-3 specification is not public. So I can't copy/paste part of the text. I will use Wikipedia instead.For T = 1: maximum block size the card can receive. Encodes IFSC.

If T = 15: supported supply voltages and low power modes

| TA3 | # | % |

|---|---|---|

| 1379 | 66.55 % | |

| 0xFE | 388 | 18.73 % |

| 0xC7 | 109 | 5.26 % |

| 0xC3 | 35 | 1.69 % |

| 0x80 | 24 | 1.16 % |

| 0x20 | 19 | 0.92 % |

| 0x43 | 14 | 0.68 % |

| 0x3C | 9 | 0.43 % |

| 0x47 | 8 | 0.39 % |

| 0x86 | 7 | 0.34 % |

| 0xA0 | 7 | 0.34 % |

| 0x00 | 6 | 0.29 % |

| 0x03 | 6 | 0.29 % |

| 0x50 | 6 | 0.29 % |

| 0x42 | 5 | 0.24 % |

| 0xC6 | 5 | 0.24 % |

| 0x40 | 4 | 0.19 % |

| 0x60 | 4 | 0.19 % |

| 0x70 | 4 | 0.19 % |

| 0x66 | 3 | 0.14 % |

| 0x90 | 3 | 0.14 % |

| 0xFC | 3 | 0.14 % |

| 0xFF | 3 | 0.14 % |

| 0x46 | 2 | 0.10 % |

| 0x76 | 2 | 0.10 % |

| 0xF0 | 2 | 0.10 % |

| 0xFA | 2 | 0.10 % |

| 0xFB | 2 | 0.10 % |

| 0x07 | 1 | 0.05 % |

| 0x26 | 1 | 0.05 % |

| 0x3A | 1 | 0.05 % |

| 0x3D | 1 | 0.05 % |

| 0x52 | 1 | 0.05 % |

| 0x64 | 1 | 0.05 % |

| 0x7C | 1 | 0.05 % |

| 0x83 | 1 | 0.05 % |

| 0x87 | 1 | 0.05 % |

| 0xC2 | 1 | 0.05 % |

| 0xEF | 1 | 0.05 % |

The interpretation of TA3 depends on the protocol in use.

19% of ATRs have TA3 = 0xFE :

- In most case the interpretation is that TA3 gives the value of IFSC (maximum size of information field of blocks that can be received by the card) for T=1. One example is 3B 97 11 C0 FF B1 FE 35 1F 83 A5 05 01 01 02 A3 01 5F with IFSC = 0xFE or 254 bytes.

- For 2 ATRs AT3 gives the supported supply voltages and low power modes for T=0. One example is 3B D9 18 00 C0 09 10 FE 54 59 46 4F 4E 45 00 00 00

IFSC

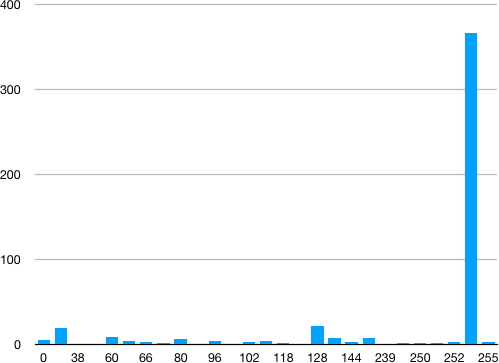

The IFSC repartition is as follows:| IFSC | # | % |

|---|---|---|

| 254 | 366 | 75,78 % |

| 128 | 21 | 4,35 % |

| 32 | 19 | 3,93 % |

| 60 | 9 | 1,86 % |

| 134 | 7 | 1,45 % |

| 160 | 7 | 1,45 % |

| 80 | 6 | 1,24 % |

| 0 | 5 | 1,04 % |

| 64 | 4 | 0,83 % |

| 96 | 4 | 0,83 % |

| 112 | 4 | 0,83 % |

| 66 | 3 | 0,62 % |

| 102 | 3 | 0,62 % |

| 144 | 3 | 0,62 % |

| 252 | 3 | 0,62 % |

| 255 | 3 | 0,62 % |

| 70 | 2 | 0,41 % |

| 118 | 2 | 0,41 % |

| 240 | 2 | 0,41 % |

| 250 | 2 | 0,41 % |

| 251 | 2 | 0,41 % |

| 38 | 1 | 0,21 % |

| 58 | 1 | 0,21 % |

| 82 | 1 | 0,21 % |

| 100 | 1 | 0,21 % |

| 124 | 1 | 0,21 % |

| 239 | 1 | 0,21 % |

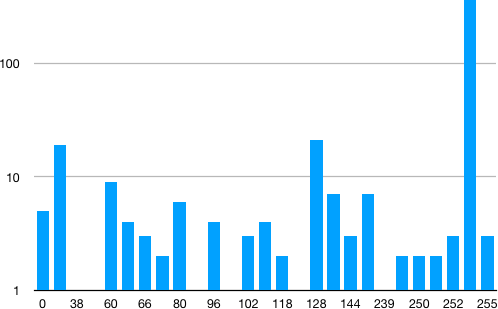

With a logarithmic scale:

75% of ATRs with a IFSC defined in TA3 (so T=1 cards only) defines IFSC = 254.

Supported supply voltages

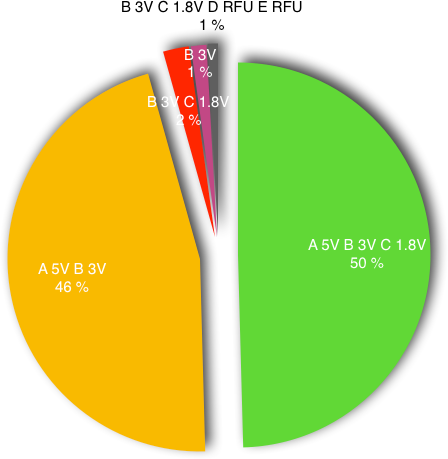

It is also possible to get the repartition of the class:| Class | # | % |

|---|---|---|

| A 5V B 3V C 1.8V | 114 | 49,57 % |

| A 5V B 3V | 106 | 46,09 % |

| B 3V C 1.8V | 5 | 2,17 % |

| B 3V | 3 | 1,30 % |

| B 3V C 1.8V D RFU E RFU | 2 | 0,87 % |

50% of ATRs defining the class supports the 3 classes: A, B and C for 5 Volts, 3 Volts and 1.8 Volt.

46% of ATRs defining the class supports the classes A and B but not C.

2 cards declare the support of classes D and E that are RFU. They are 3B D9 18 00 C0 09 10 FE 54 59 46 4F 4E 45 00 00 00 and 3B DD 96 00 80 10 FE 80 31 80 63 01 FF C0 73 B3 21 1B 81 05. It may be a bug in the parsing since the class is defined only after T=15 protocol. But in the two examples the latest defined protocol is T=0. The ATRs may not be valid.